## 國立中山大學九十七學年度第二學期資工系數位系統期末考試題

## 學號:

姓名:

一、選擇與是非題(每題4分,40分)

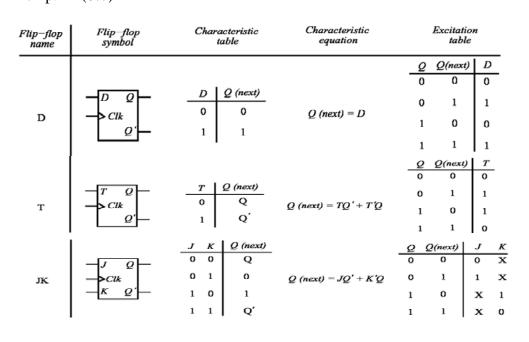

- ( ) 1. What kind of flip-flop is the most popular component to compose a register?  $\bigcirc SR \oslash D \oslash JK \oplus T$

- ( ) 2 What kind of flip-flop is the most popular component to compose an asynchronous counter?  $@SR @D @JK \oplus T \circ$

- ( ) 3. Compared with a synchronous counter, which one is the main weakness of the asynchronous counter? ①longer delay ②larger cost (area) ③larger power consumption ④more difficult to design

- What kind of storage component usually merges the input data bus and output data bus into a bi-direction I/O bus to reduce the number of I/O pins? ①Register file ②ROM ③RAM ④FIFO

- ) 5. How many address lines are required in a 16M×16 RAM? ①16 ②20 ③24 ④28

- ( ) 6. The BCD counter can be achieved by a 4-bit up/down counter with parallel load. The '0' must be loaded when count direction is down and counter content is 9.

- ( ) 7. To extend the address space (increase the number of memory words), a larger RAM can be composed of some smaller RAMs with parallel connection (並聯).

- ( ) 8. Compared with RAM, register file has shorter access time and smaller capacity (memory words).

- ( ) 9. The control unit in a digital system is a sequential circuit and it can be regarded as a finite state machine (FSM).

- ( ) 10. The datapath in a digital system is a combinatorial circuit.

二、問答題(80分)

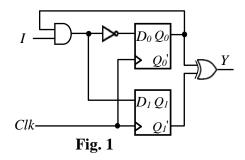

- **1.** Derive (a) excitation equations, (b) a next-state equation, (c) a state/output table, and (d) a state diagram for the circuit shown in Fig. 1. (18%)

- **2**. Using the synthesis procedure for FSM models, design a synchronous counter that counts in the sequence 0, 1, 3, 5, 0, 1, 3, 5, ..., using natural binary encoding as shown in Fig. 2 and: (a) D flip-flops (b) JK flip-flops. (18%)

- **3**. Design a 4-bit register that can load new data and swap the most-significant and least-significant bits as shown in Table 1. (10%)

- **4.** Construct a 4-bit asynchronous counter using: (a) T flip-flops (b) D flip-flops. (12%)

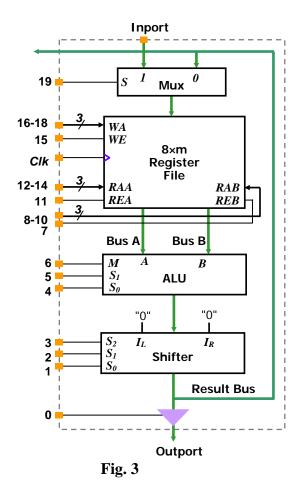

- 5. (1) Please fill in the blanks in Table 2 with the control words of one's counter example. (14%)

(2) Please describe the operation of the datapath shown in Fig. 3 to perform Ocount := 0 and Ocount := Ocount + Temp. (8%)

| 0XNo Change $Q_3 Q_2 Q_1 Q_0$ 10Load Input $I_3 I_2 I_1 I_0$ | $S_1$ | $S_0$ | Operation  | Next State        |

|--------------------------------------------------------------|-------|-------|------------|-------------------|

|                                                              | 0     | Х     | No Change  | $Q_3 Q_2 Q_1 Q_0$ |

| 1 1 0 0 0 0 0                                                | 1     | 0     | Load Input | $I_3 I_2 I_1 I_0$ |

| I I Swap $Q_1 Q_0 Q_3 Q_2$                                   | 1     | 1     | Swap       | $Q_1 Q_0 Q_3 Q_2$ |

| Table 1 |  |

|---------|--|

|---------|--|

Data => R1

Mask => R2 Ocount => R3

Temp => R4

| Contro.<br>Words | l<br>IE | Write<br>address | Read<br>address A | Read<br>address B | ALU<br>operation | Shifter<br>operation | OE |

|------------------|---------|------------------|-------------------|-------------------|------------------|----------------------|----|

| 1                | 1       | R1               | х                 | х                 | х                | х                    | 0  |

| 2                | 0       | R3               | R0                | R0                | add              | pass                 | 0  |

| 3                | 0       |                  |                   |                   |                  |                      | 0  |

| 4                | 0       |                  |                   |                   |                  | _                    | 0  |

| 5                | 0       |                  |                   |                   |                  |                      | 0  |

| 6                | 0       |                  |                   |                   |                  |                      | 0  |

| 7                | 0       | none             | R3                | 0                 | add              | pass                 | 1  |

Table 2

- 2. Ocount := 0 3. Mask := 1

- while Data :≠ 0 repeat Temp := Data AND Mask

- 4.

- Ocount : = Ocount + Temp Data := Data >> 1 5.

- 6.

- end while

- 7. Output := Ocount

| S                               | $_2 S_1$                             | $S_{\theta}$                         | Shift Operations                                                                    |

|---------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>1<br>1<br>1      | 0<br>0<br>1<br>1<br>0<br>0           | 0<br>1<br>0<br>1<br>0<br>1<br>0      | pass<br>pass<br>not used<br>not used<br>shift left<br>rotate left<br>shift right    |

| 1                               | 1                                    | 1                                    | rotate right                                                                        |

| М                               | $S_1$                                | S <sub>0</sub>                       | ALU Operations                                                                      |

| 0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | complement A<br>AND<br>EX-OR<br>OR<br>decrement A<br>add<br>subtract<br>increment A |